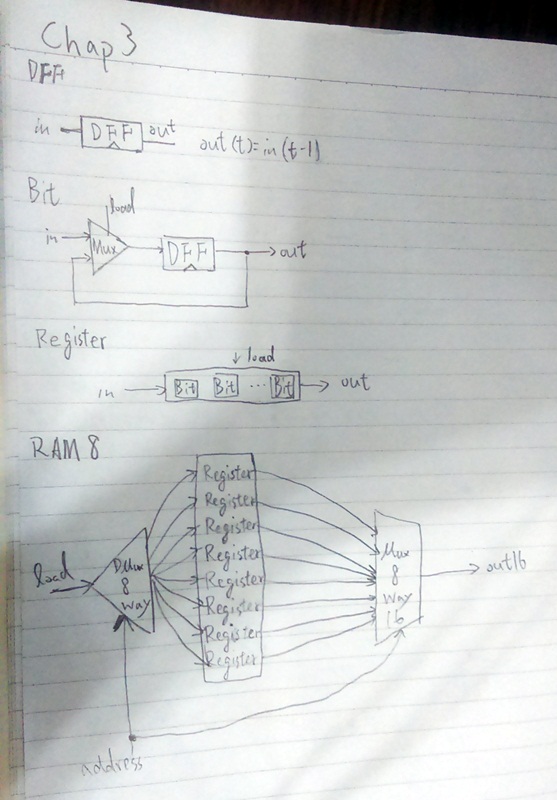

Chap 3

筆記:

作業部分:

Bit

CHIP Bit {

IN in, load;

OUT out;

PARTS:

Mux ( a=oa , b=in , sel=load , out=om );

DFF ( in=om ,out=out , out=oa );

}

Register

CHIP Register {

IN in[16], load;

OUT out[16];

PARTS:

Bit ( in=in[0] , load=load , out=out[0] );

Bit ( in=in[1] , load=load , out=out[1] );

Bit ( in=in[2] , load=load , out=out[2] );

Bit ( in=in[3] , load=load , out=out[3] );

Bit ( in=in[4] , load=load , out=out[4] );

Bit ( in=in[5] , load=load , out=out[5] );

Bit ( in=in[6] , load=load , out=out[6] );

Bit ( in=in[7] , load=load , out=out[7] );

Bit ( in=in[8] , load=load , out=out[8] );

Bit ( in=in[9] , load=load , out=out[9] );

Bit ( in=in[10] , load=load , out=out[10] );

Bit ( in=in[11] , load=load , out=out[11] );

Bit ( in=in[12] , load=load , out=out[12] );

Bit ( in=in[13] , load=load , out=out[13] );

Bit ( in=in[14] , load=load , out=out[14] );

Bit ( in=in[15] , load=load , out=out[15] );

}

RAM8

CHIP RAM8 {

IN in[16], load, address[3];

OUT out[16];

PARTS:

DMux8Way ( in=load , sel=address , a=ia , b=ib , c=ic , d=id , e=ie , f=if , g=ig , h=ih );

Register ( in=in , load=ia , out=o0 );

Register ( in=in , load=ib , out=o1 );

Register ( in=in , load=ic , out=o2 );

Register ( in=in , load=id , out=o3 );

Register ( in=in , load=ie , out=o4 );

Register ( in=in , load=if , out=o5 );

Register ( in=in , load=ig , out=o6 );

Register ( in=in , load=ih , out=o7 );

Mux8Way16 ( a=o0 , b=o1 , c=o2 , d=o3 , e=o4 , f=o5 , g=o6 , h=o7 , sel=address , out=out );

}

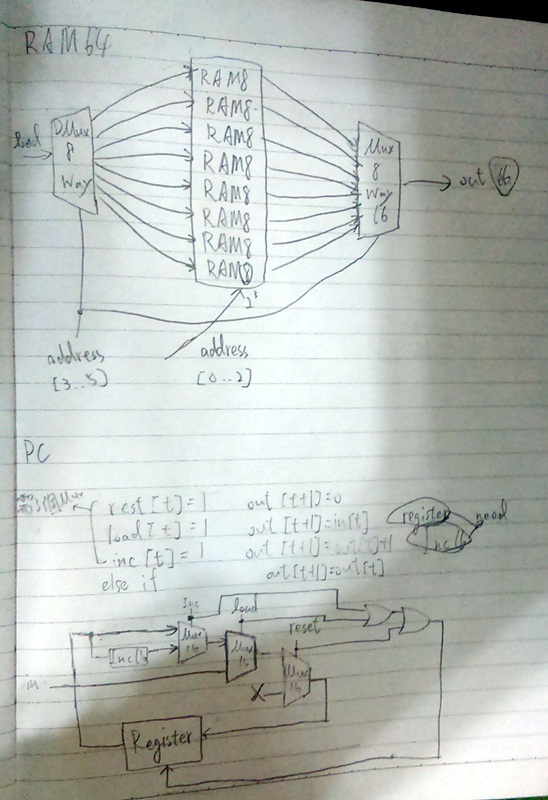

RAM64

CHIP RAM64 {

IN in[16], load, address[6];

OUT out[16];

PARTS:

DMux8Way ( in=load , sel=address[3..5] , a=ia , b=ib , c=ic , d=id , e=ie , f=if , g=ig , h=ih );

RAM8 ( in=in , load=ia , address=address[0..2] , out=o0 );

RAM8 ( in=in , load=ib , address=address[0..2] , out=o1 );

RAM8 ( in=in , load=ic , address=address[0..2] , out=o2 );

RAM8 ( in=in , load=id , address=address[0..2] , out=o3 );

RAM8 ( in=in , load=ie , address=address[0..2] , out=o4 );

RAM8 ( in=in , load=if , address=address[0..2] , out=o5 );

RAM8 ( in=in , load=ig , address=address[0..2] , out=o6 );

RAM8 ( in=in , load=ih , address=address[0..2] , out=o7 );

Mux8Way16 ( a=o0 , b=o1 , c=o2 , d=o3 , e=o4 , f=o5 , g=o6 , h=o7 , sel=address[3..5] , out=out );

}

RAM512

CHIP RAM512 {

IN in[16], load, address[9];

OUT out[16];

PARTS:

DMux8Way ( in=load , sel=address[6..8] , a=ia , b=ib , c=ic , d=id , e=ie , f=if , g=ig , h=ih );

RAM64 ( in=in , load=ia , address=address[0..5] , out=o0 );

RAM64 ( in=in , load=ib , address=address[0..5] , out=o1 );

RAM64 ( in=in , load=ic , address=address[0..5] , out=o2 );

RAM64 ( in=in , load=id , address=address[0..5] , out=o3 );

RAM64 ( in=in , load=ie , address=address[0..5] , out=o4 );

RAM64 ( in=in , load=if , address=address[0..5] , out=o5 );

RAM64 ( in=in , load=ig , address=address[0..5] , out=o6 );

RAM64 ( in=in , load=ih , address=address[0..5] , out=o7 );

Mux8Way16 ( a=o0 , b=o1 , c=o2 , d=o3 , e=o4 , f=o5 , g=o6 , h=o7 , sel=address[6..8] , out=out );

}

RAM4K

CHIP RAM4K {

IN in[16], load, address[12];

OUT out[16];

PARTS:

DMux8Way ( in=load , sel=address[9..11] , a=ia , b=ib , c=ic , d=id , e=ie , f=if , g=ig , h=ih );

RAM512 ( in=in , load=ia , address=address[0..8] , out=o0 );

RAM512 ( in=in , load=ib , address=address[0..8] , out=o1 );

RAM512 ( in=in , load=ic , address=address[0..8] , out=o2 );

RAM512 ( in=in , load=id , address=address[0..8] , out=o3 );

RAM512 ( in=in , load=ie , address=address[0..8] , out=o4 );

RAM512 ( in=in , load=if , address=address[0..8] , out=o5 );

RAM512 ( in=in , load=ig , address=address[0..8] , out=o6 );

RAM512 ( in=in , load=ih , address=address[0..8] , out=o7 );

Mux8Way16 ( a=o0 , b=o1 , c=o2 , d=o3 , e=o4 , f=o5 , g=o6 , h=o7 , sel=address[9..11] , out=out );

}

RAM16K

CHIP RAM16K {

IN in[16], load, address[14];

OUT out[16];

PARTS:

DMux4Way ( in=load , sel=address[11..13] , a=ia , b=ib , c=ic , d=id );

RAM4K ( in=in , load=ia , address=address[0..10] , out=o0 );

RAM4K ( in=in , load=ib , address=address[0..10] , out=o1 );

RAM4K ( in=in , load=ic , address=address[0..10] , out=o2 );

RAM4K ( in=in , load=id , address=address[0..10] , out=o3 );

Mux4Way16 ( a=o0 , b=o1 , c=o2 , d=o3 , sel=address[11..13] , out=out )

}

PC

CHIP PC {

IN in[16],load,inc,reset;

OUT out[16];

PARTS:

Register ( in=mro , load=ilr , out=out, out=ro );

Or ( a=inc , b=load , out=ilo );

Or ( a=ilo , b=reset , out=ilr );

Inc16 ( in=ro , out=io );

Mux16 ( a=ro , b=io , sel=inc , out=mio );

Mux16 ( a=mio , b=in , sel=load , out=mlo );

Mux16 ( a=mlo , b[0..15]=false , sel=reset , out=mro );

}